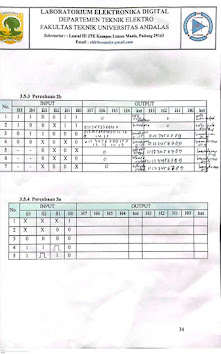

LAPORAN AKHIR PERCOBAAN 2 M3

- Analisa

kenapa output percobaan 2a mengcounter tidak beraturan!

Jawab:

Pada IC 7490 dan 7493, clock dan clk berfungsi sebagai input clock yang mengatur perubahan output pada counter. Clk adalah clock utama yang memicu perubahan hitungan dengan setiap sinyal naik-turun yang diterima, sementara clk biasanya digunakan untuk melanjutkan perhitungan atau sebagai pembagi frekuensi tambahan. Pada percobaan 2a terlihat bahwa kedua clock A dan B diberikan secara bersamaan, hal ini menyebabkan output yang dihasilkan menghasilkan bilangan biner secara acak. - Analisa

kenapa output percobaan 2b mengcounter secara berurutan?

Jawab:

Berdasarkan rangkaian yang telah dibuat, kita melihat bahwa ada perbedaan antara input clock A dan B dengan percobaan 2a. Pada percobaan 2b, dapat dilihat bahwa clock diberikan input secara seri atau secara berurutan sehingga output yang dihasilkan berurutan dari kecil hingga besar. Analisa kenapa output pada percobaan 2b pada IC 74LS90 hanya bisa mengcounter sampai 9 ?

Jawab :

IC 74LS90 adalah BCD (Binary Coded Decimal) counter, yang hanya menghitung dari 0 hingga 9 (0000 hingga 1001 dalam biner). Setelah mencapai nilai 9, counter otomatis kembali ke 0. Ini karena IC ini memiliki pembatas internal yang menyebabkan output kembali ke nilai awal setelah mencapai batas hitungan 9, sesuai dengan format BCD.

Analisa kenapa output pada percobaan 2b pada IC 7493 bisa mengcounter sampai 15 ? Jawab: berbeda dengan IC74LS90 yang mampu mereset otomatis saat hitungan mencapai 9,IC 7493 ini memiliki kemampuan menghitunh hingga 15 dikarenakan pengaruh inputannya yang dipengaruhi oleh CLK A dan CLK B tanpa dilengkapi pin reset manual yang mengakibatkan output yang dikeluarkan akan menghitung hingga bit 1111 hal ini berbeda dengan percobaan 2a yang mampu reset otomatis pada hitungan 9

Komentar

Posting Komentar